-

Posts

11 -

Joined

-

Last visited

Content Type

Profiles

Forums

Downloads

Gallery

Posts posted by Ratataplam

-

-

Hi all,

I'm moving the first steps in TS world and I try to communicate with a VI runs in asynchronous mode. First of all seem that I able to stop the VI at end of sequence, but I cannot read\write data from TS. To make simple the problem, I fixed a constant in my VI and connected it to indicator, mapping the indicator on TS parameter. In the TS sequence I check the value of TS parameter, but the result is different from the expected. Where is my mistake?

Thanks for any suggestions

p.s. LV2018 and TS2017SP1 was used to generate the problem 😃

-

7 hours ago, JKSH said:

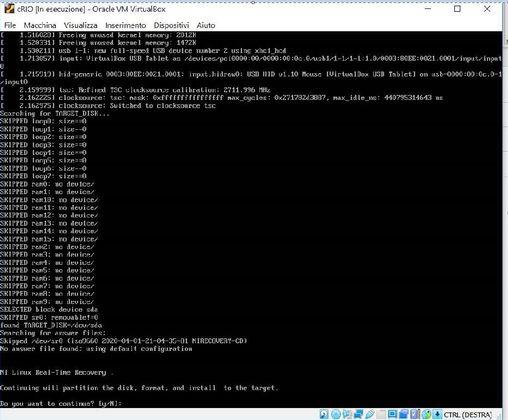

You're almost there. The NI Linux Real-Time Recovery system is incompatible with the VM's keyboard^.

When you reach the prompt, "Do you want to continue? [y/N]", make sure you have a physical USB keyboard connected to your PC. "Insert" it into your VM (on English VirtualBox, it's Devices > USB > [Name of USB Keyboard]), then use the USB keyboard to enter "y". You might need to try different keyboards; I found that:

- Microsoft Wired Keyboard 600 did not work

- Logitech K235 worked

^Earlier, you were able to select "Verbose mode" with the VM keyboard because you were still in the GRUB bootloader, not in the NI Linux Real-Time Recovery system yet. GRUB is compatible with the VM's keyboard.

Hi, thanks for the support.

The first attempts were done with embedded keyboard (I' use a laptop) and today with external usb keyboard, but the result is the same. :(

-

Hi all

I need to test my LV RT update without real target (cRIO-9045) and I don't need to use the real I/O module and real FPGA, I want to test only the interface betwwen host application (on PC) and RT application (cRIO).

To do that I've used

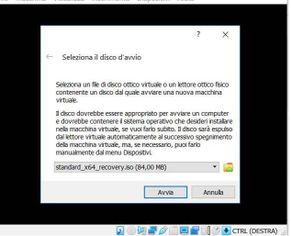

1) "ni-linux-rt-pxi-system-image-2019.09_19.5_online_repack2.exe"

to download the iso file : standard_x64_recovery.iso (84 MB)

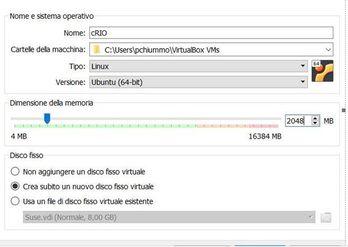

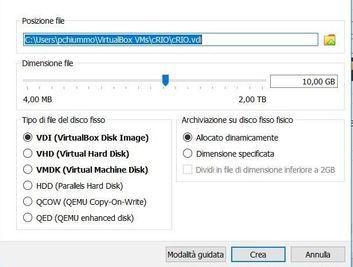

2) After I 've Created a VM with Oracle VM 6.1 + “Oracle_VM_VirtualBox_Extension_Pack-6.1.12.vbox-extpack”

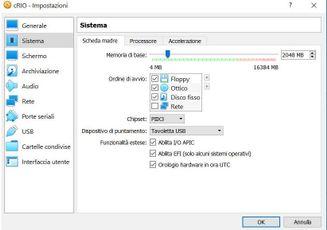

Below the VM settings :a) Linux Ubuntu 64bit and 2GB RAM b) 10 GB

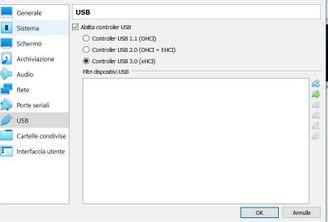

c) EFI selected d) USB 3 controller for keyboard

e) selected the *.iso file

3) after run ("avvia") and with keyboard arrow select "verbose mode" (keep in mind, the keyboards now works)

but when the installation arrives at the first choice option I'm not able to select anything because the keyboards on VM doesn't work

Any suggestion?

Thanks

-

Hi all,

I'm a beginner with VS (Veristand), stimuls profile and real time seq.

I nedd to introduce in my test a ramp, I found a ramp under Real-Time Sequence Library->Waveforms folder.

The function required :

- RampOut—The variable to ramp from the InitialValue to the FinalValue.

- InitialValue—The starting value from which to start ramping.

- FinalValue—The ending value.

- Duration—The duration in seconds over which to ramp RampOut.

My RampOut parameters (Temp2) is a I32 and the ramp accept only double, so the editor generate an error :

"The expression Temp2 in of type int32 but is passed a reference into a reference parameter of type Double in Ramp(Tem2,0,100,20). Reference parameters must match exactly"

How can 'cast' Temp2 in ramp function?

Thanks

-

Thanks Infinitenothing

-

Thanks at all, both solution works.

My question is an academic question. If I connect the sine wave generator to AO port or to Multiply operator a "cast" (red dot) is used by LV. Now, I must certificated my project and the assessor could be ask something about the red dot so how I can demonstrate that I don't not loss the information ? One solution is the test as decribed by "infinitenothing" or logical approach as suggest by Jordan. Does exist the way to avoid the cast without change the HW settings?

Regards

-

Hi all,

i try to generate a sinewave in FPGA (NI cRIO Platform), to do that I use the specific VI (Sine Wave Generator) for fpga to produce a sinewave in UINT16 data type.

Unfortunatelly my AO module works with FXP data type (see attach) and I need to adaptd the UINT16 to AO module.

A simple cast is not sufficent because I loss information, any suggestion ?

-

Hi,

simple the cRIO is already present in the lab :D

-

14 hours ago, smithd said:

Not sure if this was a typo, but RT-FIFOs are between loops on the RT side. You would use a Host-to-Target FPGA FIFO to pass data down to the FPGA for output. These fifo types do not support clusters, so you'd have to develop your own scheme for passing data down. This may be as simple as sending values in chunks of N, but you do have to watch out for overflows.

If you are sending data from RT to FPGA there is a likelihood of underflow, depending on the output rate. You would probably wish to load all your file data into the fifo first and then tell the FPGA to start reading. This all depends of course on how much data you have. If you have 10 minutes of data at a rate of 1 Hz, this is overkill but would still work. If you have 10 minutes of data at 100 kHz, then you likely won't have enough memory, so you'll want to preload the FIFO and then feed data as fast as you can.

You'll also want to keep in mind the signals side of this. I'm not great in this area, but I would imagine that you are attempting to replicate a continuous signal, you'll want to output as fast as possible to reduce frequency spikes as the output changes.

thanks a lot, your suggestions have avoid several attempt

-

Hi all,

I need your opinion about a problem.

I need to reproduce a data file on a cRIO. Typically the file is made of recorded data from the field with at least 2 columns : time and value. I would use a cRIO to reproduce the file and stimulate my target (device under test) with the same condition of the equipment on the filed.The idea is :

1) trasfer the file on cRIO file system and open it.

2) read the data from the file with Read Delimited Spreadsheet and save the value in an array

3) read the array, row-by-row, with an auto-indexed tunel loop

4) Inside the loop send the data, organized into a cluster, to cRIO FPGA via RT-FIFO

5) On FPGA keep in listen on the RT-read and get the message when readySomeone has experience in this case? Any suggestion?

Thanks

Comunication with asynchronous VI

in TestStand

Posted

Hi all, yes.

I've implemented a APIs, LV queue based, to Tx\Rx message.