Search the Community

Showing results for tags 'simulation'.

-

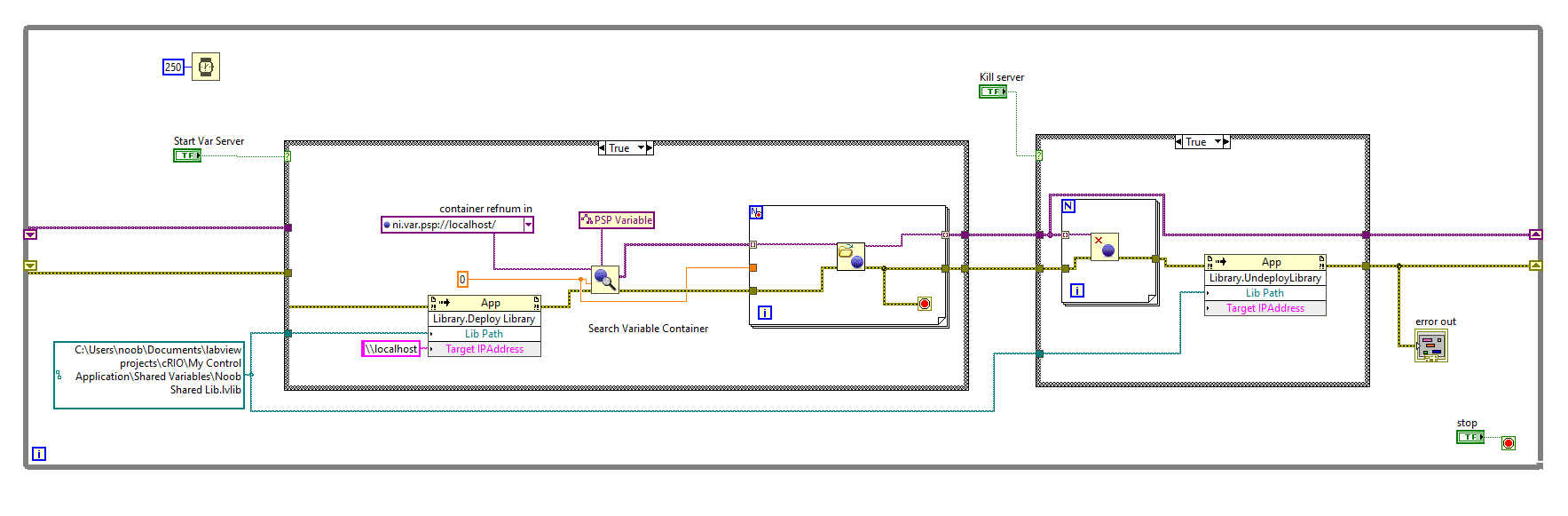

Hello hope you can help, (did edit this text to make it better to understand) Normal testcode (If I have more time I can try to include this code) I try to simulate the real time main in a cRIO test project. All goes well I can run the real time main on "my computer" target and use the FPGA in simulation mode without the use of real hardware. when I add an extra loop to the real time main with new shared variables which are not used in the simulated FPGA, I can not deploy anymore. In that case I can only deploy when I use the option disable auto deploy variables (right mouse on RT compact RIO target) and make the variables absolute (right mouse on the variable in the blockdiagram code). but when I run with this option I get an error -1950679035 when I want to use the shared variables which are *not* used in the FPGA. I Use a desktop execution node to change data on the simulated FPGA this works fine. Smaller code without the FPGA I made the code smaller and easier to understand to have focus on the shared network variables, this code is included below . There is a screenshot and the real code. When I use the small program and try to load the *non* FPGA shared variables, I get the same error -1950679035. when I only use the shared variables which are previous used in the FPGA vi and remove the non FPGA shared variables all is okay, I can also see the FPGA variables in the in the Ni Distributed system manager. Although the other program simulating the total cRIO code with FPGA has long been stopped. What I want is to open a library with a link to the file e.g.: C : \folder with *.vlib . But I am unable to open a direct link to the harddrive e.g.: C:\Users\noob\Documents\labview projects\cRIO\My Control Application\Shared Variables\Noob Shared Lib.lvlib I get the error -1950679035 again. I only do not get errors when I try to acces network shared variables I did previous use in the test with the FPGA simulation and where where used in the FPGA code. I think the desktop execution node only adds shared network variables from the FPGA code to the Ni variable server and does not do this for the shared network variables in the Real time main code. I am able to see the old FPGA shared network variables when I use the NI Distributed System Manager which can be found at the tools menu. I think I must load a variable library into the server before I can acces it with the code below is this correct? Can anyone point me in the correct direction to do this? hope you guys can help and I hope this text is easier to understand compared to the text I wrote last night 🙂 at nights it tends to be late and my texts show that. If the question is not clear please let me know then I will try to solve it. Hope you guys can help thanx! Enable Debug modus.vi

-

Hello, I found an example of an On-Off controller on Labview that I am attaching. I wanted to see how it would work the same VI replacing the thermostat a PID block and using the simplified model of a room in the form of the transfer function (R / (RCS +1)) but I'm not sure the right way to proceed. the integrator is to stay? I have to connect directly with the pid of the entrance to the furnace? I have to modify the VI? I hope in your kind suggestion thanks Alessandro On-Off Controller modificato.vi On-Off Controller.vi

-

Now I'm suing Control Design and Simulation, I would like to ask that if I'm created Transfer function in the Simulation, and I want to convert to Control Design, by using CD Convert from Simulation to Control Design.vi, how can I use it? please recommence me, thanks.

-

Hi guys, just wondering if it is possible to publish a web service with a control and simulation loop in the vi. I have a simulation loop and an output of an array and matrix of data from a signal, yet i can't seem to be able to deploy the vi at all. It will build but not deploy. Any help or advice would be most appreciated. Thanks

-

Hi, I am trying to tabulate data into a form such that i can display data points from a signal into an array that ultimately can be displayed graphically in a restful web service. Iv'e been able to simulate data via a waveform indicator using a simple simulate signal vi, but i can't seem to find a solution anywhere that will allow me to extract and display points from a signal from within a simulation loop. I've tried using the indexer funtion which seems to be limited and using the collector funtion which I am struggling to get to grips with. If anyone could help me find a solution or give me advice on how to go about solving this problem I would appreciate it so much! Thanks, Christian controlloop.vi