Search the Community

Showing results for tags 'fifo'.

-

I have a system that composed of 1- NI-cRIO9014 2- Chassis (cRIO-9104) 3- Three Mods. NI9215 I use this system to capture 12 analog signals. What is the relation between sampling frequency defined by time delay in fpga.vi and the Requested number of Elements defined in FIFO?. When I use a time delay of 40us and Requested number of Elements 8191, it produces wrong data. When I use a time delay of 40us and Requested number of Elements 65535, it produces correct data.

-

I have a system that composed of 1- NI-cRIO9014 2- Chassis (cRIO-9104) 3- Three Mods. NI9215 The following are properties of my current FPGA Target Class: cRIO-9104 FPGA Device Information: Family: Virtex-II Type: xc2v3000 Speed Grade: -4 Package: fg676 Compiler Information: Version: Xilinx 10.1 Xilinx Options in Build Specifications: Supported Host Computer/FPGA Communication: Programmatic FPGA Interface Communication: Supported Interactive Front Panel Communication: Supported Number of Logical Interrupts: 32 DMA: Number of DMA Channels: 3 Multi-Element Access on Target: Not supported Peer-to-Peer Streaming: Not supported Type: Target to Host - DMA Control logic: Slice Fabric I am reading 12 Analog signals, I do not know what is the maximum value for Requested Number of Elements I can use? The General page help says a size of 2^M-1, What is M?

-

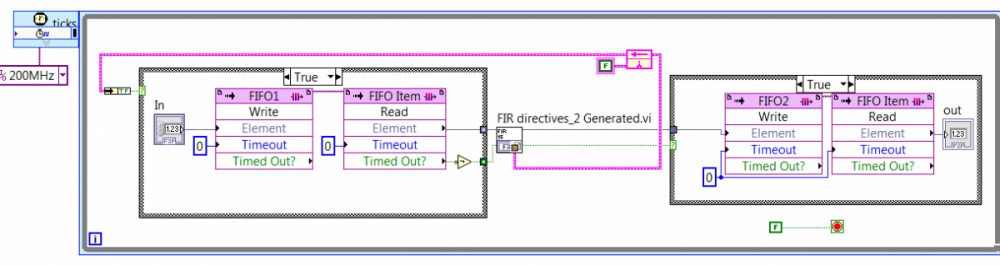

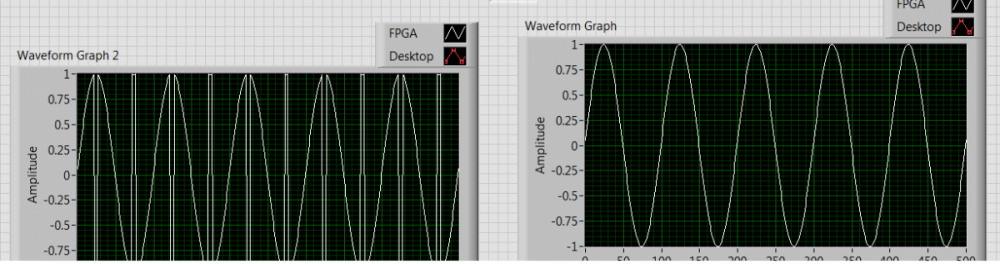

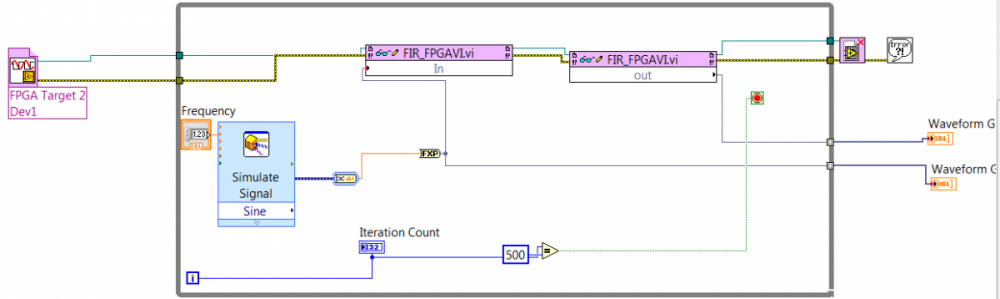

I am having trouble realising an FIR filter in Spartan 3E XUP board. I have succesfully compiled the FPGA VI generated from "Generate IP" (However, IP Builder sub menu is not existing this board in Project explorer as given in FPGA IP bulider tutorial). The FPGA Vi wil be running in SCTL receiving FXP data elements. But an array of data is required for the filtering to happen. How to do this without DMA FIFO as the board supports only Target scoped FIFO?

-

- spartan 3e

- labview fpga

-

(and 2 more)

Tagged with:

-

Dear All, I have a question regarding to FPGA FIFO, specifically DMA from Host to Target (FPGA). As an Example, I have a 1D array containing 10x2000 elements stored inside the host side Buffer. At the FPGA side, I want to use 'host to target-read' to read fixed amount of elements from the host side buffer, for example exact 2000 elements. Moreover I want to hold onto the data (2000 elements) for a certain amount of time (example 10s) before reading again 2000 elements from the buffer. Does anyone have a clue how to do this? Thank you so much! Yang