Search the Community

Showing results for tags 'dma'.

-

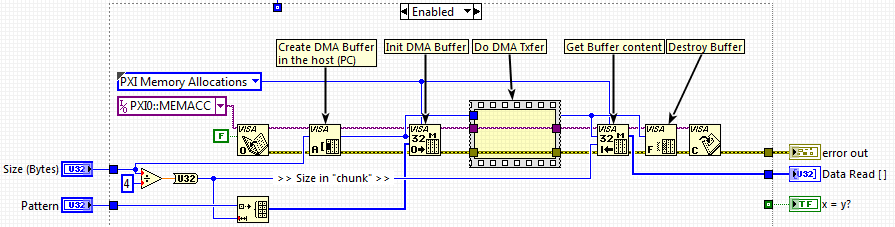

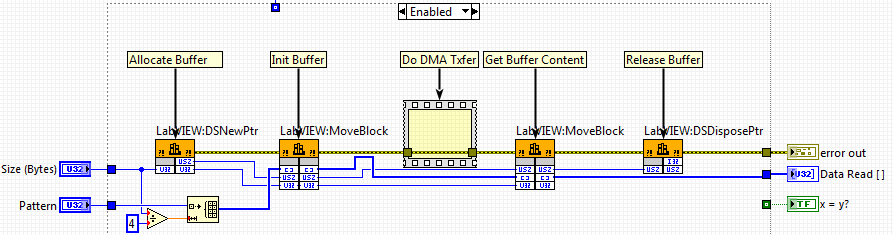

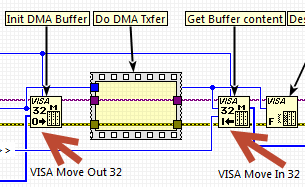

Hi We have an application where we need to have a custom PCIe board transfer data to the PC using DMA. We are able to get this to work using NI-VISA Driver Wizard for PXI/PCI board. The recommended approach is to have VISA allocate memory on the host (PC) and have the PCIe board write to it (as seen below). While this approach works well, the memory allocated by VISA for this task is quite limited (~ around 1-2MB) and we would like to expand this to tens of MB. Note: The documentation (and help available on the web) regarding these advanced VISA function (for instance "VISA Move out 32" and "VISA Move In 32") is parse. If someone has some deep knowledge regarding theses, please feel free to share how we could allocate more memory. Since we are not able to allocate more memory using the VISA function at this time, we investigate doing the same operation using the LabVIEW Memory Manager Functions which allow us to allocate much larger memory block. Below is the resulting code. Unfortunately while we can validate that reading and writing to memory using this work well outside the context of DMA transfer, doing a DMA transfer do NOT work (although the board think it did and the computer is not crashing). We are wondering why this is not working and would welcome any feedback. Note: the DMA transfer implemented on the board requires contiguous memory for it to be successful. I believe that the LabVIEW Memory Manager Functions do allocate continuous memory, but correct me if I am wrong. To troubleshoot this, I did allocate memory using the LabVIEW memory manager function and try to read it back using VISA and I got a "wrong offset" error (Note: This test may not be significant) Another data point; while the documentation for DSNewPtr do not talk about DMA transfer, the one for DSNewAlignedHandle does. Experiment using LV memory manager Handles has not got us anywhere either. We would welcome any feedback regarding either approach and about the LabVIEW Memory Manager Functions capabilities in that use case. Thanks in advance. PJM Note: We are using LabVIEW 2014 if that matter at all.

- 2 replies

-

- labview memory manager

- dma

-

(and 2 more)

Tagged with:

-

I have a system that composed of 1- NI-cRIO9014 2- Chassis (cRIO-9104) 3- Three Mods. NI9215 I use this system to capture 12 analog signals. What is the relation between sampling frequency defined by time delay in fpga.vi and the Requested number of Elements defined in FIFO?. When I use a time delay of 40us and Requested number of Elements 8191, it produces wrong data. When I use a time delay of 40us and Requested number of Elements 65535, it produces correct data.

-

Hello! Is there anything similar to "DMA MEMORY" that behaves like DMA FIFO, but without the FIFO part? I would like to transfer 1000 bytes of data from the FPGA to the cRIO host and 1000 bytes of data from the host to the FPGA and I don't care about old data - I only need the latest data. Ideally I would like to have two pieces of memory, each 1000 bytes long. One piece that can be written from the FPGA and read from the host and the other piece that can be written by the host and read by the FPGA, so that the first byte of data is always on the address 0. DMA FIFO is not a viable solution, because I would like to get the data as fast as possible, but I can read it on the host only on certain non deterministic intervals. If I would use the DMA FIFO, I would need a huge FIFO to store all the unused old measurements. Thank you for any reply or suggestion. Kind regards, Greg

-

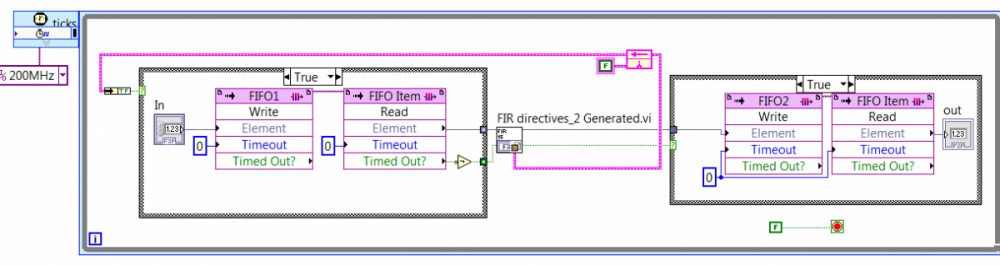

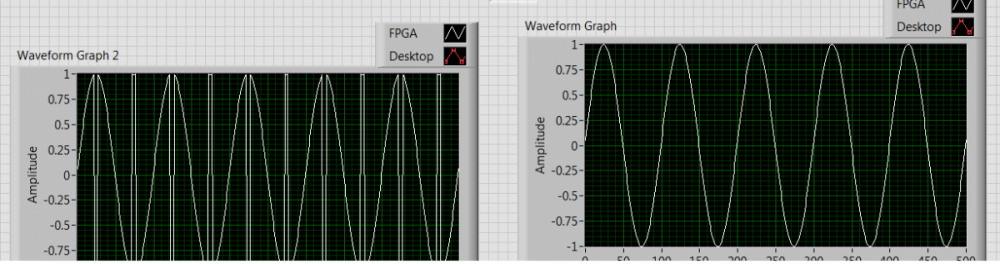

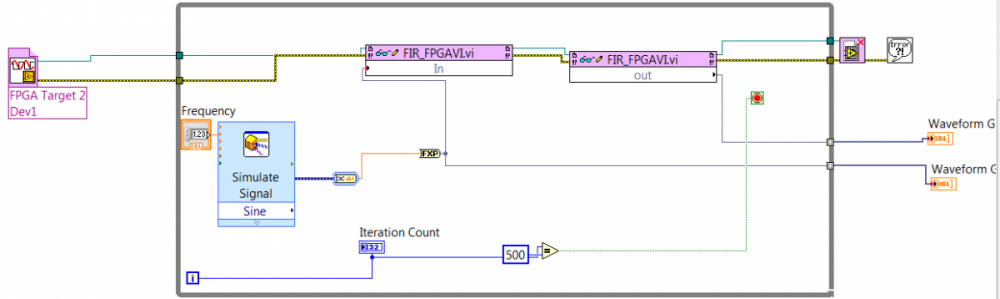

I am having trouble realising an FIR filter in Spartan 3E XUP board. I have succesfully compiled the FPGA VI generated from "Generate IP" (However, IP Builder sub menu is not existing this board in Project explorer as given in FPGA IP bulider tutorial). The FPGA Vi wil be running in SCTL receiving FXP data elements. But an array of data is required for the filtering to happen. How to do this without DMA FIFO as the board supports only Target scoped FIFO?

-

- spartan 3e

- labview fpga

-

(and 2 more)

Tagged with:

-

Dear All, I have a question regarding to FPGA FIFO, specifically DMA from Host to Target (FPGA). As an Example, I have a 1D array containing 10x2000 elements stored inside the host side Buffer. At the FPGA side, I want to use 'host to target-read' to read fixed amount of elements from the host side buffer, for example exact 2000 elements. Moreover I want to hold onto the data (2000 elements) for a certain amount of time (example 10s) before reading again 2000 elements from the buffer. Does anyone have a clue how to do this? Thank you so much! Yang

-

Hi everyone, I will be presenting TS1360: "Implementing an Efficient Moving Average Filter in LabVIEW FPGA" on Thursday 1-2pm. Room 16B. These techniques are relevant for developing any sort of code on the FPGA, not necessarily filters. Many of the findings are a bit counter-intuitive for someone used to developing regular LabVIEW code or even Real-Time LabVIEW code. Hope to see some of you there or bump into you in the corridors of the Convention Centre! Cheers, Neville.