-

Posts

596 -

Joined

-

Last visited

-

Days Won

26

Content Type

Profiles

Forums

Downloads

Gallery

Everything posted by ensegre

-

Ctl reedited is invalid after saved

ensegre replied to Vandy_Gan's topic in LabVIEW Community Edition

And must you really do it in a compiled executable? Cosmetic properties you can change programmatically on the fly even in an exe. -

Ctl reedited is invalid after saved

ensegre replied to Vandy_Gan's topic in LabVIEW Community Edition

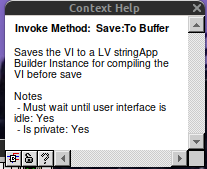

I would have said why don't you use Save.Instrument which is a public method, but I see that it is not supported in runtime, and that is stated expressly. A fortiori, a private method which "must wait until the user interface isidle" might be a completely IDE thing. -

Ctl reedited is invalid after saved

ensegre replied to Vandy_Gan's topic in LabVIEW Community Edition

I do not know what is a LV stringApp instance, but I doubt that it is exactly a loadable control. What are you trying to achieve exactly? -

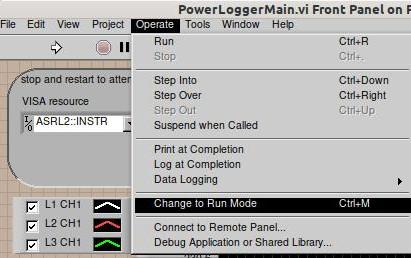

How to save preview version in runtime

ensegre replied to Vandy_Gan's topic in LabVIEW Community Edition

-

Help saving a newer LabVIEW project for an older version of LabVIEW

ensegre replied to JBC's topic in LabVIEW General

There should be a forum on the dark side for that, but anyway, here you go. LabGRAD_21.zip -

How to load a base64-encoded image in LabVIEW?

ensegre replied to Harris Hu's topic in LabVIEW General

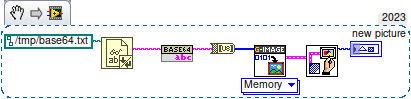

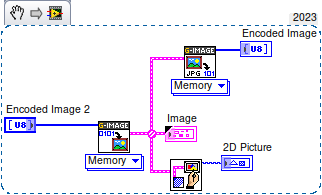

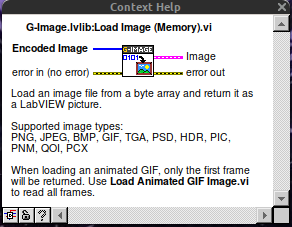

So in LV>=20, using OpenSerializer.Base64 and G-Image. That simple. Linux just does not have IMAQ. Well, who said that the result should be an IMAQ image? -

How to load a base64-encoded image in LabVIEW?

ensegre replied to Harris Hu's topic in LabVIEW General

Where do you get that from? -

How to load a base64-encoded image in LabVIEW?

ensegre replied to Harris Hu's topic in LabVIEW General

-

How to load a base64-encoded image in LabVIEW?

ensegre replied to Harris Hu's topic in LabVIEW General

I haven't yet really looked into, but why not just wrapping libjpeg, instead of endeavoring the didactic exercise of G-reinventing of the wheel? -

How to load a base64-encoded image in LabVIEW?

ensegre replied to Harris Hu's topic in LabVIEW General

You could also check https://github.com/ISISSynchGroup/mjpeg-reader which provides a .Net solution (not tried). So, who volunteers for something working on linux? -

How to load a base64-encoded image in LabVIEW?

ensegre replied to Harris Hu's topic in LabVIEW General

As for converting jpg streams in memory, very long time ago I have used https://forums.ni.com/t5/Example-Code/jpeg-string-to-picture/ta-p/3529632 (windows only). At the end of the discussion thread there, @dadreamer refers to https://forums.ni.com/t5/Machine-Vision/Convert-JPEG-image-in-memory-to-Imaq-Image/m-p/3786705#M51129, which links to an alternative WinAPI way. -

How to load a base64-encoded image in LabVIEW?

ensegre replied to Harris Hu's topic in LabVIEW General

I haven't tried any of them, but these are the first 3 results popping up from a web search: https://forums.ni.com/t5/Example-Code/LabVIEW-Utility-VIs-for-Base64-and-Base32Hex-Encoding-Using/ta-p/3491477 https://www.vipm.io/package/labview_open_source_project_lib_serializer_base64/ https://github.com/LabVIEW-Open-Source/Serializer.Addons (apparently the repo of the code of the previous one) -

What are some choices for producer-consumer protocols?

ensegre replied to Reds's topic in LabVIEW General

Redis is certainly high performance and suited to multiple, loose writers, readers and subscribers, with bindings for so many ecosystems. One of its several features, which I haven't perused, are Streams. I'd be curious too to know whether continuous cross-app data streaming could be efficiently implemented using them. -

So I have been given this monster FPGA project to patch. The main target VI is a monster with a BD of 9034x10913px, with 72 different loops . Yes there is some documentation an comments, but that does not really cut it. The logic uses I haven't counted how many tens or hundreds of different FIFOs and memory locations, read and written by this or that loop of the hyerarchy. Why, Why, don't I have a"Find all instances" for FIFOs , like there is for VIs, to navigate them?

-

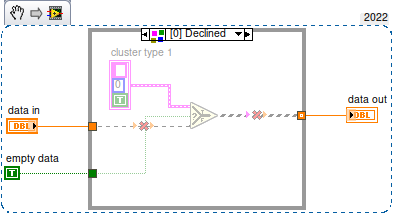

Maybe the question is if you have to be committed to this array of clusters of string+variant for some specific reason, or if it is an attempt to implement some architecture which might have a different implementation. I.e., I don't understand if yours is a general question about design, or a specific question about the mechanics of converting variants to data.

-

Serial Communication Question, Please

ensegre replied to jmltinc's topic in Remote Control, Monitoring and the Internet

i.e. crossover cable vs. null modem cable. But the OP says that the exe succeeds with the command, so that doesn't seem to be the issue here. -

Serial Communication Question, Please

ensegre replied to jmltinc's topic in Remote Control, Monitoring and the Internet

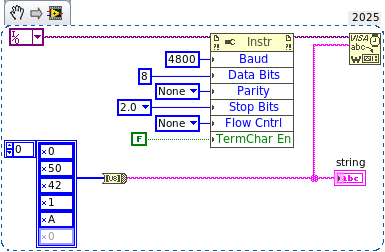

Just to make sure - if you read 5 bytes, you get the first 5 bytes. If you increase the number to 'byte count', you would get a timeout warning if the other program really outputs only 5 bytes, but you would see the trailing ones, if there were. Also, right-click the string indicator, check 'Hex display' may come handy. -

Serial Communication Question, Please

ensegre replied to jmltinc's topic in Remote Control, Monitoring and the Internet

Can't say without seeing the rig's documentation (if at all good) and some amount of trial and error. These old devices may be quirky when it comes to response times (the internal uP has to interpret and to effect the command) and protocol requirements. Are you sure the message does not require an EOT or a checksum of some sort? Does the rig respond with some kind of ACK or error, which you could read back? Are you sure of your BCD encoding? Wikipedia lists so many flavours of it: https://en.wikipedia.org/wiki/Binary-coded_decimal If there are read commands, returning a known value, like the current frequency or the radio model, I would start with them, to make sure that the handshake works as expected. -

Serial Communication Question, Please

ensegre replied to jmltinc's topic in Remote Control, Monitoring and the Internet

-

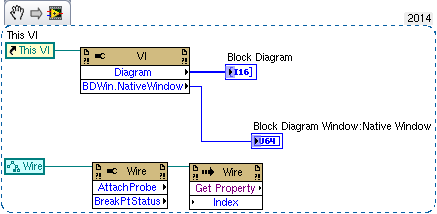

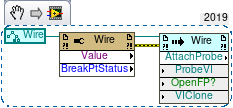

This is the situation in 14 and 19 here. In 14 Wire has some interesting properties in 14, but not Value. Note that e.g. Attach Probe is accessed as a property in 14 and a Method in 19; and BD is an array of integers in 14.

- 16 replies

-

- breakpoints

- wire values

-

(and 2 more)

Tagged with:

-

Rolf is correct, I forgot to enable scripting in the LV19 I used to check OTOH, in LV14 "Block diagram" is indeed present but is an array of I6 rather than a ref. I can't guess what was its intended use back then, maybe it was just an uncooked feature.

- 16 replies

-

- breakpoints

- wire values

-

(and 2 more)

Tagged with: